4 Core Set Associative Cache Coherence

4-Core Set Associative Cache Coherence System with MESI Protocol

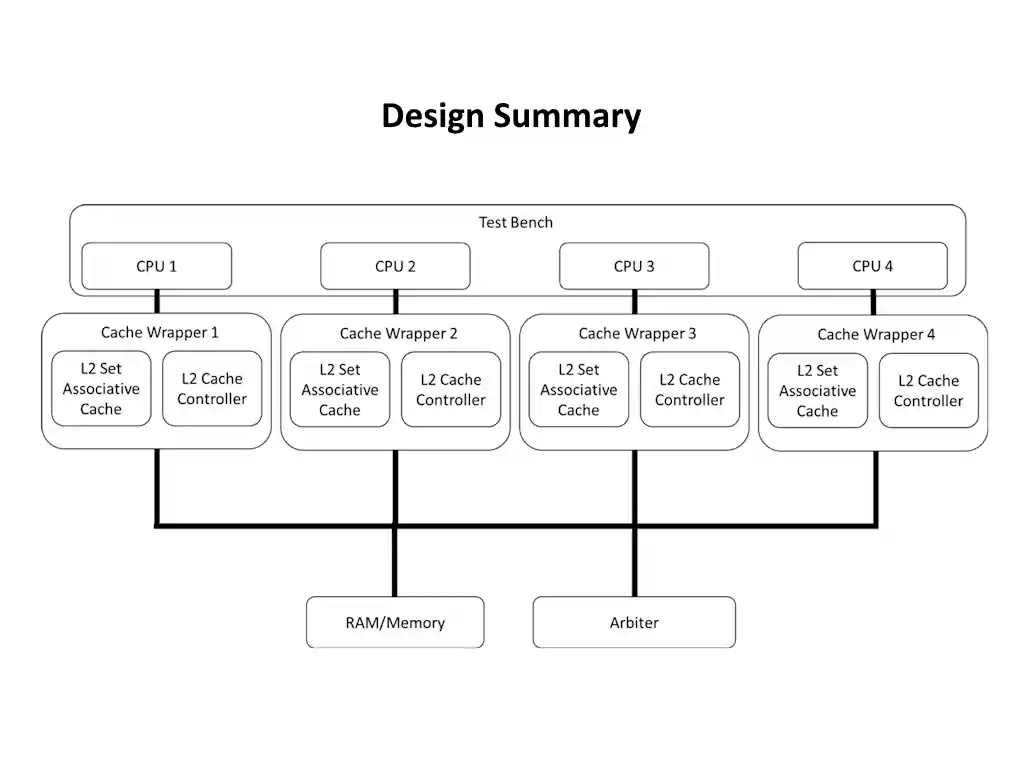

This project involved the design, implementation, and validation of a multi-core cache coherence system using a 4-way set-associative L2 cache and the MESI (Modified, Exclusive, Shared, Invalid) protocol. Key deliverables included hierarchical SystemVerilog development, bus arbitration logic, snooping-based coherence management, and comprehensive testbench validation. The system ensures data consistency across four processor cores through state transitions, invalidation signals, and shared memory synchronization.

Objectives

- Design a scalable 4-core system with set-associative L2 caches and a shared RAM module, supporting 32-bit addressing and 128-bit data blocks.

- Implement the MESI protocol to manage cache state transitions (Invalid → Modified → Shared → Exclusive) during read/write operations.

- Develop an arbiter module to resolve bus contention and prioritize snoop/processor requests for efficient shared memory access.

- Validate coherence using test vectors simulating multi-core writes, reads, and invalidation scenarios.

- Verify system behavior through RTL simulation, waveform analysis, and synthesis using ModelSim and Quartus Prime.

Project Process

- System Architecture & Module Design: Defined a hierarchical structure with four Cache Wrapper modules (L1/L2 integration), a shared RAM, and a centralized Arbiter. Implemented snooping logic to broadcast BusRd, BusRdX, and Invalidate signals across cores.

-

MESI Protocol Integration:

Designed the

L2CacheControllerto manage state transitions using combinational logic. Added pseudo-LRU replacement policies for cache misses and write-back mechanisms for Modified states. - Arbiter & Bus Logic: Developed a priority-based arbiter to resolve simultaneous bus requests (e.g., Cache 1 write vs. Cache 2 snoop). Ensured deterministic grants using a lowest-index-first policy.

-

Testbench Development:

Created test vectors to simulate cross-core conflicts (e.g., Cache 1 writes

0xCAFEBABE, Cache 2 overwrites with0xDEADBEEF, triggering Invalid → Modified transitions). Validated data consistency via waveform analysis. - Verification & Debugging: Analyzed RTL schematics to confirm signal routing between caches, RAM, and the arbiter. Verified MESI state transitions using simulation logs and memory dumps.

Conclusion and Future Improvements

The system successfully maintained cache coherence across four cores, resolving write conflicts and ensuring data consistency through MESI state transitions. Future work could expand the design to 8 cores, integrate a direct-mapped L1 cache, or implement MOESI protocol for reduced bus traffic. Enhancing test vectors to include cache eviction scenarios and multi-block transactions would further validate robustness.

Project Information

- Category: Design/Hardware

- Client: Rensselaer Polytechnic Institute

- Project date: 10 March, 2025

- Project PDF: Download MEMO