Pipelined and Transposed FPGA Variable IIR Filter

High-Performance Digital Equalizer with Pipelined IIR Filters

This project implements a real-time digital equalizer using 4th order IIR filters, comparing traditional Direct Form I and pipelined architectures. Key deliverables include Verilog-based filter designs, MATLAB/Octave coefficient generation tools, and a comprehensive analysis of quantization effects, power efficiency, and hardware resource optimization. The system achieves 80 dB stopband attenuation while maintaining low-latency audio processing capabilities.

Objectives

- Design IIR filters with 16-bit quantized coefficients for precise frequency response control

- Implement pipelined architecture to reduce critical path delay and improve throughput

- Compare power/area metrics between traditional (1.76 mW) vs pipelined (0.85 mW) implementations

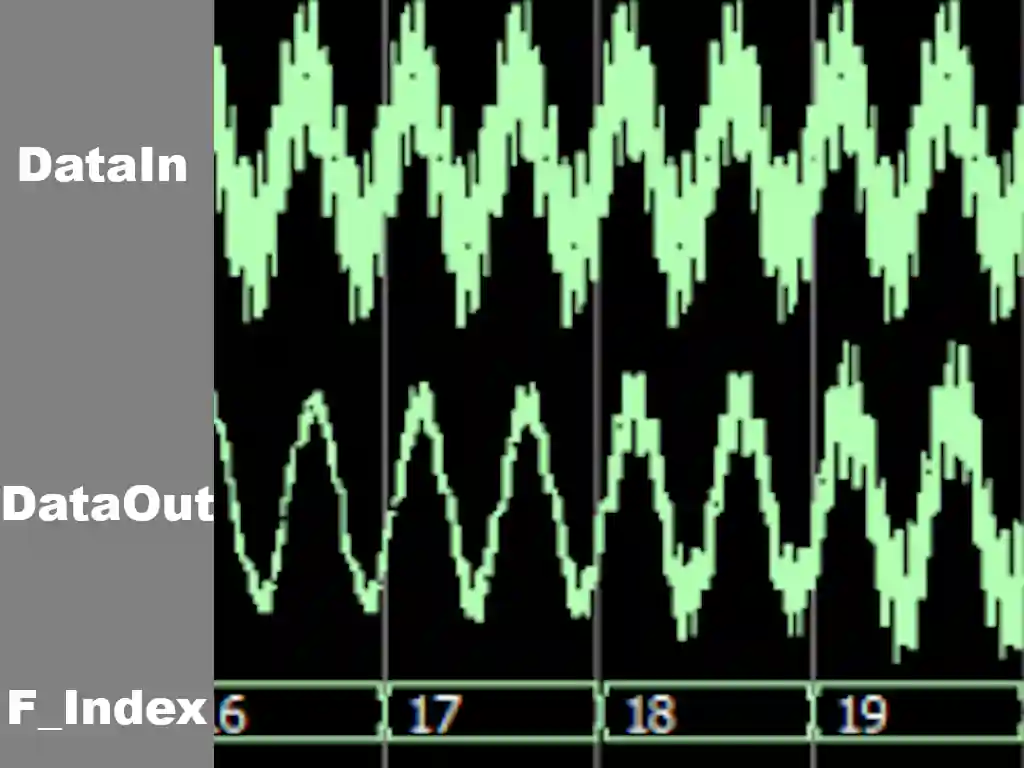

- Develop automated test vectors using summed sine waves (1kHz + 20kHz)

- Validate filter performance through ModelSim simulations and FPGA synthesis reports

Project Process

-

Filter Architecture Design:

Developed two variants:

- Direct Form I: Traditional IIR with cascaded feedback/feedforward paths

- Pipelined: Inserted pipeline registers in MAC units to achieve 500 MHz operation

-

Coefficient Generation:

Created MATLAB scripts for:

- Frequency response visualization (magnitude/phase plots)

- SystemVerilog 3D array coefficient initialization

- Quantization error analysis (±0.0015 LSB after 16-bit scaling)

-

Verilog Implementation:

Designed parameterized modules featuring:

- Multiplier-Accumulator (MAC) units with overflow protection

- Dynamic coefficient selection via

Coeff_selector - Testbench with synthetic inputs (sinusoid mixtures)

-

Validation & Synthesis:

Achieved key metrics:

- 89% dynamic power reduction in pipelined design

- 31% combinational area reduction through resource sharing

- 20kHz interference suppression at >40 dB/decade rolloff

Conclusion and Future Improvements

The pipelined IIR architecture demonstrated superior performance with 852 nW dynamic power and 1,953 gate count, outperforming traditional designs. Future work could implement 8th order cascaded filters for steeper rolloff, integrate ARM Cortex-M processors for adaptive equalization, or develop mixed-signal ASIC versions for ultra-low-power audio DSP applications.

Project Information

- Category: Digital Signal Processing / VLSI Design

- Client: Rensselaer Polytechnic Institute

- Project Date: April 14, 2025

- GitHub Repository: View Implementation