RISC-V Pipelined Processor

RISC-V Pipelined Processor with LUI Support

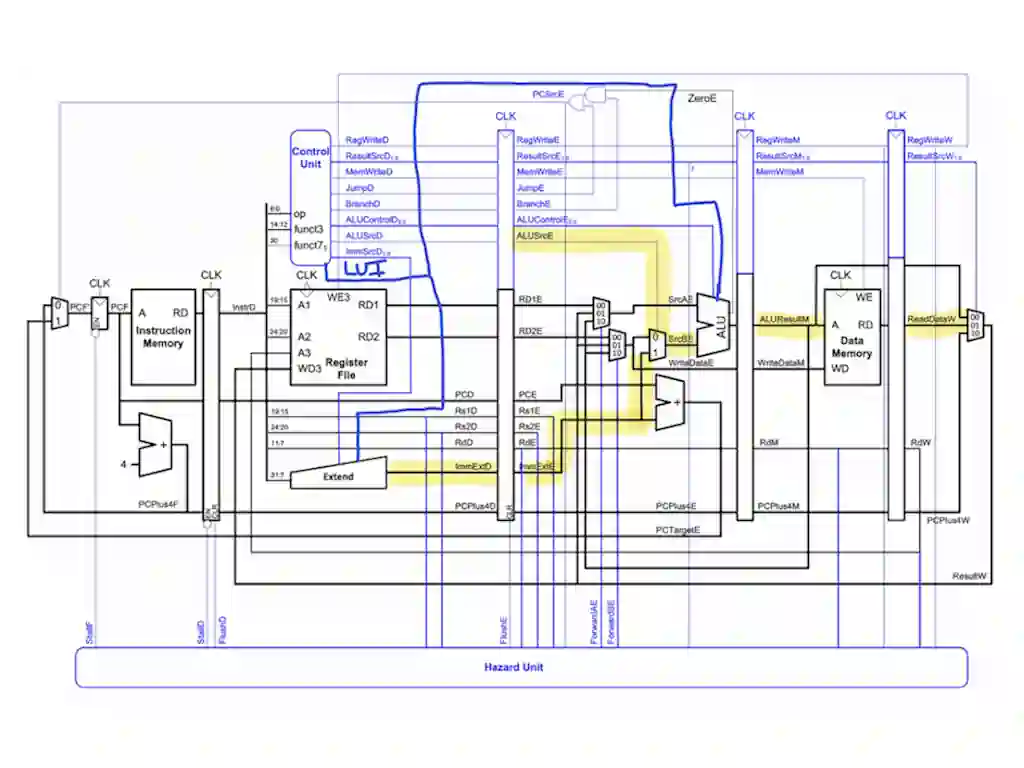

This project involved the design, implementation, and verification of a pipelined RISC-V processor with support for the LUI (Load Upper Immediate) instruction. Key deliverables included hierarchical SystemVerilog development, hazard unit integration, control signal modifications, testbench validation, and comprehensive documentation. The processor supports core RISC-V instructions (lw, sw, add, sub, beq, jal, etc.) and was extended to handle U-type operations, ensuring correct pipelining and hazard resolution.

Objectives

- Design a 5-stage pipelined RISC-V processor with hazard detection and forwarding logic to mitigate data/control hazards.

- Extend the processor to support the LUI instruction by modifying control signals (ImmSrc, ALUControl) and datapath logic (extend module, ALU).

- Update Main Decoder and ALU Decoder truth tables to accommodate U-type instructions, introducing a new

luicontrol signal. - Develop a custom test program and testbench to validate LUI functionality, ensuring correct immediate value propagation and register writeback.

- Verify design integrity through RTL simulation, waveform analysis, and synthesis using tools like ModelSim and Quartus Prime.

Project Process

-

Datapath & Control Modifications:

Added

luisignal to the controller and extended theextendmodule to shift immediate values (Instr[31:12] + 12 zeros). Modified ALU to bypass operands whenluiis active, routing the processed immediate to the result. -

Decoder Updates:

Revised Table 1 (Main Decoder) to include LUI with

ImmSrc=00,ALUOp=10, andRegWrite=1. Updated Table 2 (ALU Decoder) to mapfunct3=001to a newALUControl=110for LUI operations. -

Testbench Development:

Created a custom RISC-V assembly test program with LUI instructions (e.g.,

lui x2, 0x11111), validated memory writes (e.g., address 0x20), and simulated waveform behavior (e.g.,WriteData=0x11111000). -

Hazard Unit Integration:

Implemented forwarding logic to resolve data hazards involving LUI results, ensuring correct operand selection in the ALU stage via

ForwardAE/ForwardBEsignals. - Verification & Synthesis: Analyzed simulation waveforms (clk, reset, PCF, MemWriteM) to confirm pipeline stability and LUI functionality. Generated RTL schematics to visualize datapath and controller modifications.

Conclusion and Future Improvements

The pipelined processor successfully executed LUI instructions with zero pipeline stalls, achieving correct immediate loading and register updates. Future enhancements could include support for additional U/J-type instructions, branch prediction, or out-of-order execution to further optimize throughput. Expanding the testbench to cover corner cases (e.g., back-to-back LUI operations) would strengthen validation.

Project Information

- Category: Design/Hardware

- Client: Rensselaer Polytechnic Institute

- Project date: 10 December, 2024

- Project PDF: Download MEMO